Register Instructions

In this section, we will briefly describe the necessary hardware and its interconnection in order to realise register-to-register instructions. Note that the lab exercise with LogiSim will provide you with more details.

Which instructions?

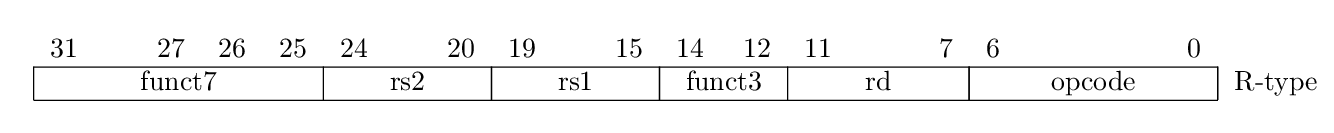

In this section, we will implement R-type instructions:

This includes the following individual instructions:

- add (addition)

- sub (subtraction)

- sll (shift left logical)

- slt (set less than)

- sltu (set less than unsigned)

- xor (bit-wise exclusive or)

- srl (shift right logical)

- or (bit-wise or)

- and (bit-wise and)

All of the above instructions share the same opcode (0110011), the type of the operation is determined by the two fields funct7 and funct3.

What do they do?

Each of these instructions takes two register values, performs some logical or arithmetic computation on them and stores the result in a register.

Most of the operations should be self explaining. The two shift operations sll

and srl will shift the bits of the first register by the number of positions

indicated by the second register1.

The instruction slt (set less than) compares the two register values and

stores a 1 in the destination register if the first value is less than the

second one, otherwise it will store 0. The instruction stlu does the same but

it interprets the register values as unsigned integers.

What do we need?

There is three things that we need to implement:

- The arithmetic and logic unit (ALU), which is left as an exercise;

- The decode unit, which has already been described in the previous section;

- The wiring of the data path, putting all the components together in a meaningful way.

Let's look at the data path, described in the following.

The data path

At this point, we already have all the individual hardware components needed to realise R-type instructions. The figure below shows how they are connected and how the different parts relate to the execution phases of an instruction:

- fetch: The PC is fed into the instruction memory, returning the current instruction word.

- decode: The instruction word is split up into the individual fields.

- execute: The operands are read from the register file and sent to the ALU.

- write back: The result from the ALU is stored in the register file.

- next instruction: We add 4 to the current PC and store the value in the PC.

Note that all of the above phases happen within the same clock cycle. The next instruction address is calculated in parallel to the reading of instruction word from memory, but the PC is only updated at the next rising edge of the clock.

The term logical shift in the case of srl means that the most

significant bits will be filled with zeros. There is also an arithmetic right

shift instruction (sra), which copies the sign bit, which is consistent with

dividing the value by a power of two. The sra instruction is not treated in

this lecture.