# IP PARIS

# **Boolean Algebra to Arithmetic**

INF107

Tarik Graba Ulrich Kühne Guillaume Duc 2023-06

# **Boolean Algebra**

#### Logic variable

A logic variable takes on one of two values: 0 (false) or 1 (true)

#### Logic functions

A logic function takes one or more logic variables as inputs and returns 0 or 1:

$$\begin{cases} \{0,1\} \times \{0,1\} \dots \times \{0,1\} \to \{0,1\} \\ e_0,e_1,\dots,e_n \to s = F(e_0,e_1,\dots,e_n) \end{cases}$$

In hardware, to represent the two values of a logic variable, we use:

- 2 different voltage (0 V/5 V, -12 V/+12 V...)

- 2 different electric current

- Presence/absence of light in an optical fiber

A logic function can be represented in different ways:

- With a truth table: table that lists the value of the function for all possible inputs

- With an *equation*

- With a *diagram*: a graphical representation using normalized symbols

- Using an Hardware Description Language (HDL): a computer language designed to be easily interpreted by a computer program

#### **Combinational and Sequential logic**

#### Combinational logic

The output depends only on the present value of the inputs

$$\forall t, s(t) = F(e_0(t), e_1(t), \dots, e_n(t))$$

#### Sequential logic

The output depends on the present value of the input and on the sequence of past inputs

$$s(t) = F(e_0(t), e_1(t), \dots, e_n(t), e_0(t-t_1), e_1(t-t_1) \dots)$$

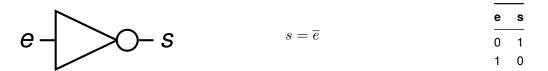

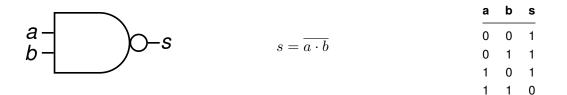

# **Basic logic gates**

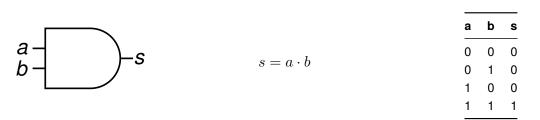

Note:  $x \cdot 0 = 0$  et  $x \cdot 1 = x$ , so an AND gate can be use to produce, from a signal x, a signal that equals to x or 0 depending on a command signal

AND

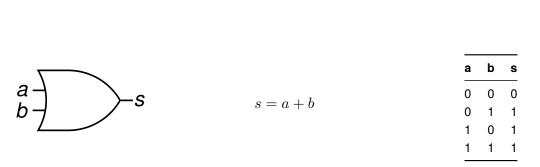

Note: x + 0 = x et x + 1 = 1, so an OR gate can be use to produce, from a signal x, a signal that equals to x or 1 depending on a command signal

OR

1

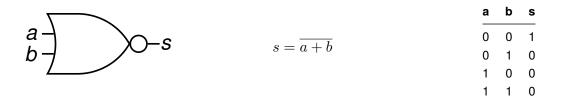

$$\overline{a+b} = \overline{a} \cdot \overline{b}$$

$$\overline{a\cdot b} = \overline{a} + \overline{b}$$

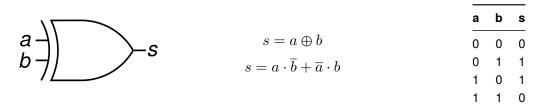

# XOR (Exclusive OR)

Note:  $x \oplus 0 = x$  et  $x \oplus 1 = \overline{x}$ , so an XOR gate can be use to produce, from a signal x, a signal that equals to x or  $\overline{x}$  depending on a command signal

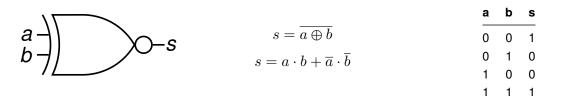

### XNOR (Not Exclusive OR, Equality)

# More complex gates

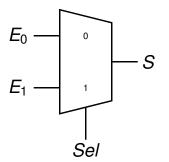

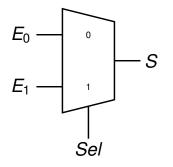

#### 2-to-1 Multiplexer

We want to build a function that selects one of its two inputs  $(E_0 \text{ or } E_1)$  depending on a third "selection" input (*Sel*):

•

$$S = E_0$$

if  $Sel = 0$

$$\bullet \ S = E_1 \text{ if } Sel = 1$$

#### 2-to-1 Multiplexer

| $S = \overline{Sel} \cdot E_0 + Sel \cdot E_1$ |

|------------------------------------------------|

| $D = DCi L_0 + DCi L_1$                        |

| Sel | $E_0$ | $E_1$ | S |

|-----|-------|-------|---|

| 0   | 0     | 0     | 0 |

| 0   | 0     | 1     | 0 |

| 0   | 1     | 0     | 1 |

| 0   | 1     | 1     | 1 |

| 1   | 0     | 0     | 0 |

| 1   | 0     | 1     | 1 |

| 1   | 1     | 0     | 0 |

| 1   | 1     | 1     | 1 |

|     |       |       |   |

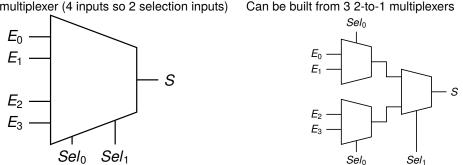

#### 4-to-1 Multiplexer

A 4-to-1 multiplexer (4 inputs so 2 selection inputs)

$S = \overline{Sel_1} \cdot \overline{Sel_0} \cdot E_0 + \overline{Sel_1} \cdot Sel_0 \cdot E_1 + Sel_1 \cdot \overline{Sel_0} \cdot E_2 + Sel_0 \cdot Sel_1 \cdot E_3$

#### n-to-1 Multiplexer

A n-to-1 multiplexer (with  $n = 2^p$ ):

- needs p selection inputs

- $\blacksquare$  can be built with n-1 2-to-1 multiplexer organized in p layers

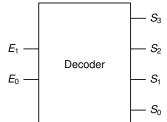

A decoder has n inputs and  $2^n$  outputs. Only one output (selected by the value of the inputs) is at 1, all others are at 0.\_\_\_\_\_

| $E_0$ | $E_1$ | $S_3$ | $S_2$ | $S_1$ | $S_0$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 1     |

| 0     | 1     | 0     | 0     | 1     | 0     |

| 1     | 0     | 0     | 1     | 0     | 0     |

| 1     | 1     | 1     | 0     | 0     | 0     |

# **Representation of numbers**

#### **Representation of positive integers**

A positive integer N can be represented in base b by a vector  $(a_{n-1}, a_{n-2}, \dots, a_1, a_0)$ , such as:

$$N = a_{n-1} \cdot b^{n-1} + a_{n-2} \cdot b^{n-2} + \ldots + a_1 \cdot b^1 + a_0 \cdot b^0$$

where:

$\blacksquare a_i \in \{0,1,\ldots,b-1\}$

•  $a_{n-1}$  is the most significant digit

•  $a_0$  is the least significant digit

## Commonly used bases

#### Binary representation of positive integers

A positive integer N can be represented in base 2 by a vector  $(a_{n-1}, a_{n-2}, \dots, a_1, a_0)$ , such as:

$$N = a_{n-1} \cdot 2^{n-1} + a_{n-2} \cdot 2^{n-2} + \ldots + a_1 \cdot 2^1 + a_0 \cdot 2^0$$

where:

- $\blacksquare a_i \in \{0,1\}$

- a<sub>i</sub> is a binary digit (bit)

- $a_{n-1}$  is the most significant bit

- $a_0$  is the least significant bit

Give the binary representation of  $54_{10}\,$

#### Conversion between binary and hexadecimal representations

In base 2 (we suppose that n is a multiple of 4):

$$N = a_{n-1} \cdot b^{n-1} + a_{n-2} \cdot b^{n-2} + \ldots + a_1 \cdot b^1 + a_0 \cdot b^0$$

As  $2^4 = 16$ , we also have:

$$N = \sum_{k=0}^{n/4-1} (a_{4k+3} \cdot 8 + a_{4k+2} \cdot 4 + a_{4k+1} \cdot 2 + a_{4k}) \cdot 16^k$$

So it is easy to convert between hexadecimal and binary representation (each hexadecimal digit corresponds to 4 bits). In addition, the hexadecimal representation is more compact than the binary representation.

$\begin{array}{l} \mbox{ Convert } 7A_{16} \mbox{ in binary} \\ \mbox{ Convert } 11111100_2 \mbox{ in hexadecimal} \end{array}$

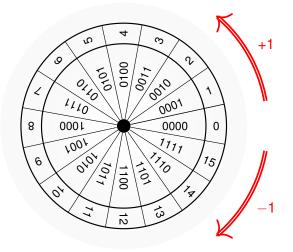

In a digital circuit (a processor for instance), the number of bits used for representing numbers is limited.

For n bits:

- There are  $2^n$  values that can be represented

- We can represent numbers in  $[0, 2^n 1]$

- Arithmetic is performed modulo  $2^n$

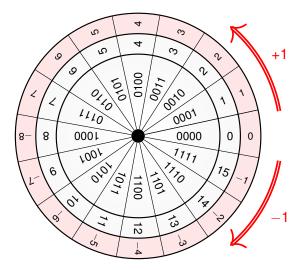

#### **Binary representation**

- $\blacksquare$  With 4 bits, we can represent numbers from 0 to  $15=2^4-1$

- The arithmetic is modulo  $2^4 = 16$ :

- 15 + 1 = 0

- 0 1 = 15

| Decimal | Binary |

|---------|--------|

| 0       | 0000   |

| 1       | 0001   |

| 2       | 0010   |

| 3       | 0011   |

| 4       | 0100   |

| 5       | 0101   |

| 6       | 0110   |

| 7       | 0111   |

- With 4 bits, we can represent numbers from 0 to  $15=2^4-1$

- The arithmetic is modulo  $2^4 = 16$ :

- 15 + 1 = 0

- 0 1 = 15

- How to keep the same behaviour and represent negative and positive integers?

| Decimal | Binary |

|---------|--------|

|         | Dinary |

| 0       | 0000   |

| 1       | 0001   |

| 2       | 0010   |

| 3       | 0011   |

| 4       | 0100   |

| 5       | 0101   |

| 6       | 0110   |

| 7       | 0111   |

| With 4 bits, we | can | represent | numbers from $\boldsymbol{0}$ |

|-----------------|-----|-----------|-------------------------------|

| to $15 = 2^4 -$ | 1   |           |                               |

- The arithmetic is modulo  $2^4 = 16$ :

- 15 + 1 = 0

- 0 1 = 15

- We can interpret 1111 as -1 instead of 15

| Decimal | Binary | Decimal | Binary |

|---------|--------|---------|--------|

| 0       | 0000   | 8       | 1000   |

| 1       | 0001   | 9       | 1001   |

| 2       | 0010   | 10      | 1010   |

| 3       | 0011   | 11      | 1011   |

| 4       | 0100   | 12      | 1100   |

| 5       | 0101   | 13      | 1101   |

| 6       | 0110   | 14      | 1110   |

| 7       | 0111   | -1      | 1111   |

- With 4 bits, we can represent numbers from 0 to  $15=2^4-1$

- The arithmetic is modulo  $2^4 = 16$ :

- 15 + 1 = 0

- 0 1 = 15

- We can interpret half the numbers as negatives

| ecimal | Binary | Decimal | Bina |

|--------|--------|---------|------|

| 0      | 0000   | -8      | 100  |

| 1      | 0001   | -7      | 100  |

| 2      | 0010   | -6      | 101  |

| 3      | 0011   | -5      | 101  |

| 4      | 0100   | -4      | 110  |

| 5      | 0101   | -3      | 110  |

| 6      | 0110   | -2      | 111  |

| 7      | 0111   | -1      | 111  |

### Two's complement

The two's complement is a way to represent signed numbers (it is the most commonly used but not the only one)

The most significant bit holds an information about the sign (0: positive, 1: negative)

The value A of an n-bit integer  $a_{N-1}a_{N-2} \dots a_0$  in two's complement is:

$$A = -a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i$$

The two's complement can represent integers in the range  $[-2^{n-1}, 2^{n-1}-1]$

- Represent -8 and +8 in two's complement

- Using 4 bits

- Using 5 bits

#### Represent -1

- Using 1 bit

- Using 2 bits

- Using 3 bits

#### Sign extension

If  $N=a_{n-1},a_{n-2},\ldots,a_0$  a signed integer represented in two's complement with n bits, how to represent N with n+1 bits?

$$N = -a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i = -a_{n-1}2^{n-1} \cdot (2-1) + \sum_{i=0}^{n-2} a_i 2^i = -a_{n-1}2^n + \sum_{i=0}^{n-1} a_i 2^i$$

So  $N=a_{n-1},a_{n-1},a_{n-2},\ldots,a_0$  with n+1 bits: the most significant bit is duplicated

### Additive inverse/The opposite

If N is a signed integer represented in two's complement with n bits, and if -N can be represented in two's complement with n bits:

$$-N = \overline{N} + 1$$

## The opposite (proof)

$$\begin{split} N &= -a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i \\ -N &= a_{n-1}2^{n-1} - \sum_{i=0}^{n-2} a_i 2^i \\ &= a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} (-a_i)2^i \end{split}$$

If b is a bit,  $(1-b=\overline{b})$  or  $(-b=-1+\overline{b}),$  so:

$$-N = a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} (-1 + \overline{a_i})2^i$$

# The opposite (proof)

\_

$$\begin{split} -N &= a_{n-1} 2^{n-1} - \sum_{i=0}^{n-2} 2^i + \sum_{i=0}^{n-2} \overline{a_i} 2^i \\ &= a_{n-1} 2^{n-1} - (2^{n-1} - 1) + \sum_{i=0}^{n-2} \overline{a_i} 2^i \\ &= (a_{n-1} - 1) 2^{n-1} + \sum_{i=0}^{n-2} \overline{a_i} 2^i + 1 \\ &= -\overline{a_{n-1}} 2^{n-1} + \sum_{i=0}^{n-2} \overline{a_i} 2^i + 1 \\ &= \overline{N} + 1 \end{split}$$

## Fixed-point

A fractional number D can be approximated in base 2 by the vector  $(a_{n-1},a_{n-2},\ldots,a_1,a_0,a_{-1}\ldots a_{-m})$  such as:

$$D = a_{n-1} \cdot 2^{n-1} + a_{n-2} \cdot 2^{n-2} + \ldots + a_1 \cdot 2^1 + a_0 \cdot 2^0 + a_{-1} \cdot 2^{-1} + \ldots a_{-m} \cdot 2^{-m}$$

where:

- $(a_{n-1}, \dots a_0)$  is the integer part

- $(a_{-1}, \dots a_{-m})$  is the fractional part

- the precision of the approximation is  $2^{-m}$

- Represent 0.5, 3.625

- Represent 0.6

- Using 1 bit

- Using 3 bits

- Using 5 bits

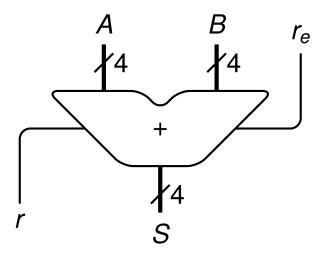

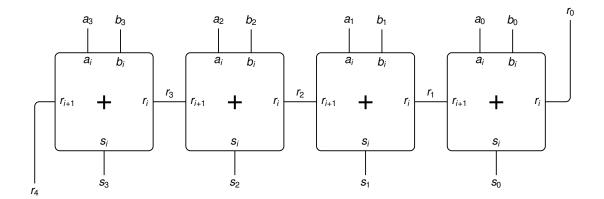

# **Arithmetic operators**

Do the addition of two 4-bit numbers

The addition of two binary numbers can be decomposed into several elementary addition on 1 bit.

# Ripple-carry adder (carry-propagate adder)

# **Ripple-carry adder**

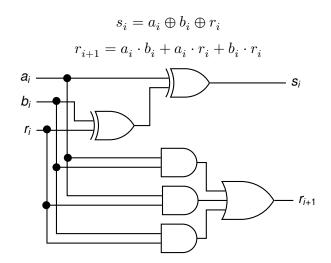

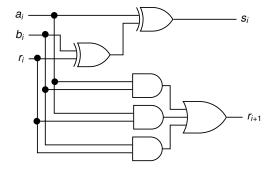

# Full adder (1 bit)

Arithmetically:  $a_i + b_i + r_i = 2 \cdot r_{i+1} + s_i$

| $\overline{a_i}$ | $b_i$ | $r_i$ | $r_{i+1}$ | $s_i$ | Decimal |

|------------------|-------|-------|-----------|-------|---------|

| 0                | 0     | 0     | 0         | 0     | 0       |

| 0                | 0     | 1     | 0         | 1     | 1       |

| 0                | 1     | 0     | 0         | 1     | 1       |

| 0                | 1     | 1     | 1         | 0     | 2       |

| 1                | 0     | 0     | 0         | 1     | 1       |

| 1                | 0     | 1     | 1         | 0     | 2       |

| 1                | 1     | 0     | 1         | 0     | 2       |

| 1                | 1     | 1     | 1         | 1     | 3       |

49/59

# Full adder (1 bit)

If A and B are two natural integers represented with n bits:

$$\begin{array}{rrrr} A & \leq & 2^n - 1 \\ B & \leq & 2^n - 1 \\ A + B & \leq & 2^{n+1} - 2 < 2^{n+1} \end{array}$$

So the result of A + B can always be represented with n + 1 bits

## Addition (two's complement)

If A and B are two integers represented in two's complement with n bits:

So the result of A + B can always be represented with n + 1 bits

#### Addition (two's complement)

Addition of two integers represented on 3 bits:

|   |   |   |   |          | unsigned | 2'sC         |

|---|---|---|---|----------|----------|--------------|

|   |   | 1 | 1 | 1        | 7        | -1           |

| + |   | 0 | 0 | 1        | 1        | 1            |

| = | 1 | 0 | 0 | 0        | 8        | 0  or  -8?   |

|   |   |   |   |          | unsigned | 2'sC         |

|   |   | 0 | 1 | 1        | 3        | 3            |

| + |   | 0 | 0 | $1 \mid$ | 1        | 1            |

| = | 1 | 1 | 0 | 0        | 4        | -4  or  + 4? |

|   |   |   |   |          | unsigned | 2'sC         |

|   |   | 1 | 1 | 1        | 7        | -1           |

| + |   | 1 | 0 | 0        | 4        | -4           |

| = | 1 | 0 | 1 | 1        | 11       | +3  or  -5?  |

INF107

There is an issue with the interpretation of the carry in two's complement.

The simple solution to always have the correct answer is to sign extend the operands to one more bit and then do the addition. The resulting carry can be discarded.

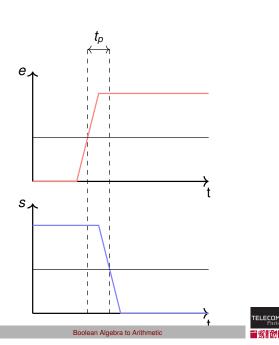

# **Propagation time**

- When the input of a gate changes, its output cannot change instantaneously.

- The propagation time is the time between the instant when the inputs of a gate change and the instant when the output of the gate stabilizes to the correct value.

- During this time, the output of a gate may be invalid (with regards to the current value of its inputs).

## Propagation time of a complex function

- For a given technology, the propagation times of basic gates are given

- From these values, we can compute the propagation time of more complex functions by adding the individual propagation time

- The propagation time of a complex function is the propagation time on the longest path

## Example: full adder

- We consider the following propagation times:

- AND and OR gates: 1 ns

- · XOR gates: 2 ns

- What is the propagation time from each inputs to each output?